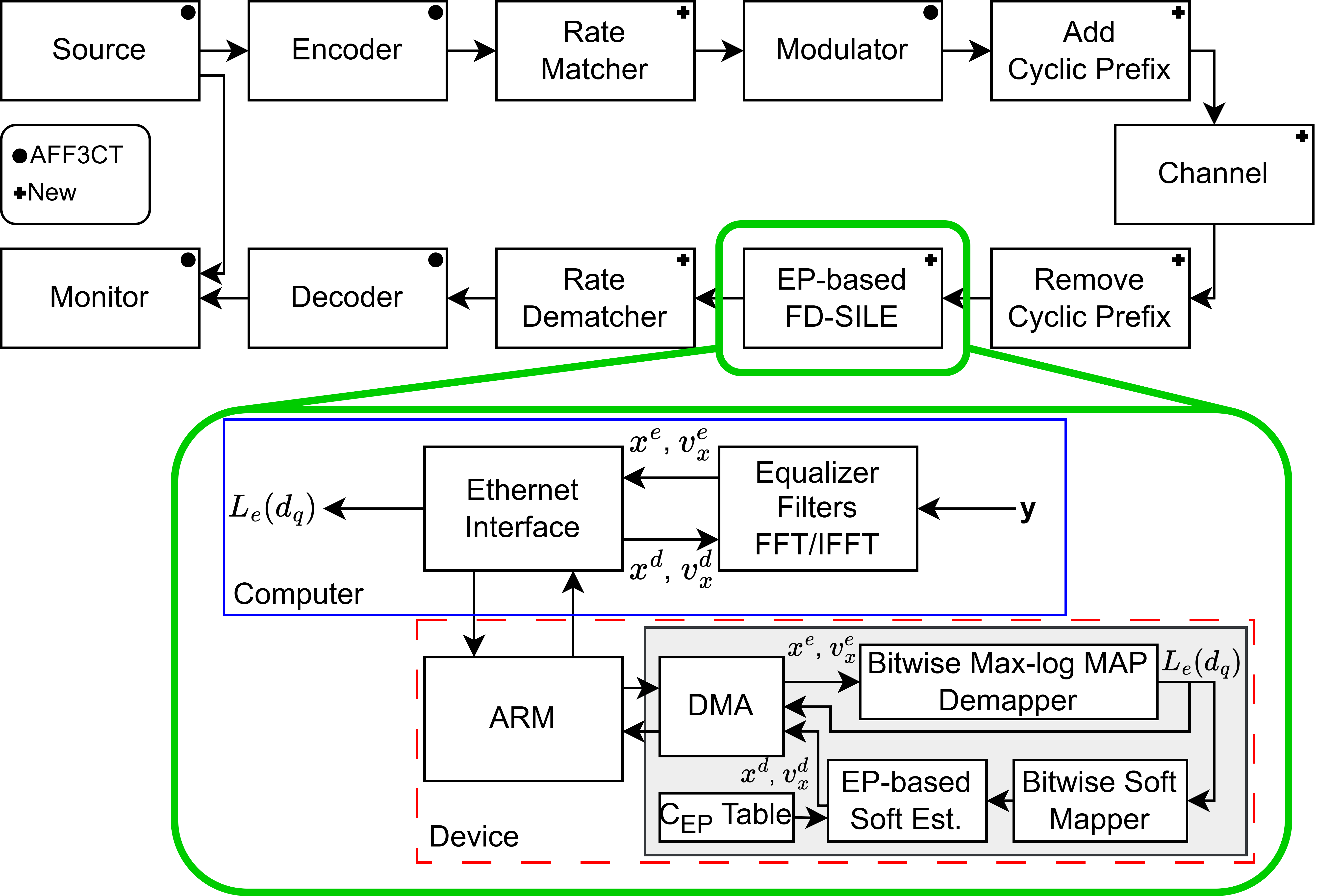

This thesis explores the design and FPGA prototyping of a digital receiver architecture based on Expectation Propagation (EP). The study focuses on a Frequency Domain Self-Iterated Linear Equalizer (FD-SILE), combining soft mapping, demapping, and equalization in a self-iterative framework. To address the computational challenges posed by high-order modulation schemes, analytical simplifications and fixed-point implementations are proposed, achieving significant reductions in complexity while maintaining robust BER performance. The research culminates in a flexible, pipelined FPGA implementation validated through Hardware-in-the-Loop (HIL) simulations, demonstrating adaptability to varying modulation schemes and real-time operational viability. This work contributes to the development of efficient, scalable receiver architectures for advanced communication systems.

News

THESIS DEFENSE of Ian FISCHER SCHILLING - March 17, 2025

Ian FISCHER SCHILLING will defend his thesis on March 17, 2025 at 10:15 am in the amphitheater F of ENSEIRB-MATMECA, on the subject: Design and FPGA Prototyping of an Advanced Receiver based on Expectation Propagation.